集成电路是由不可分离的组件组成的电路,这些组件以防止IC因建筑或商业目的而分离的方式电耦合在一起。这种电路可以使用多种技术来构建。单片集成电路现在被称为ic。

1、集成电路设计技术。

需要快速设计大型、复杂的处理器,以利用摩尔定律赋予的大量晶体管。复杂性是让巨大的芯片正常运行的障碍;许多好的芯片创意被埋没在细节的海洋中,在芯片工作之前必须解决这些细节。集成电路设计具有挑战性,因为工程师必须平衡各种问题:

2、不同程度的抽象

提炼IC的想法需要很多层的细节。设计师必须从芯片的功能规范开始,将功能扩展为架构,然后将架构扩展为逻辑设计,最后将逻辑设计扩展为版图。

3、多重且相互冲突的成本

设计师不仅必须通过多个细节层次勾勒出设计草图,还必须考虑成本不是货币费用,而是评估设计质量的标准。芯片的运行速度是一项关键成本。在执行相同任务(例如乘法)时,两种架构可以以截然不同的速率工作。将看到芯片面积是另一个关键的设计成本,因为根本无法制造大于1平方厘米的芯片,而制造芯片的成本与其面积成指数关系。此外,如果必须满足多个成本标准(例如面积和速度要求),许多设计选择将以牺牲另一个为代价来改进一个成本统计数据。平衡对立限制的做法推动了设计。

4、设计时间短

设计师将有时间考虑设计选择如何影响完美世界中的最终产品。然而,生活的世界并不完美。如果芯片发布得太晚,它们的销售额可能会因为竞争对手窃取市场份额而变得微不足道或根本不存在。因此,设计人员面临尽快制造芯片的压力。要将概念开发成功能性ASIC,在特定应用IC设计的情况下可能只有几周的时间。设计抽象和分层设计是设计师为消除无关细节而创建的两种策略。设计人员还广泛使用计算机辅助设计技术来评估和综合设计。

5、分层设计

成分

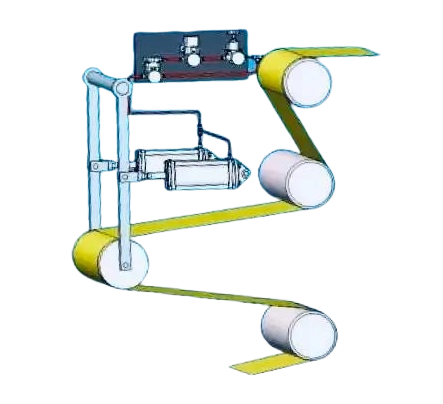

芯片设计人员可以通过将芯片分解为组件层次结构来分而治之。如下图所示,一个零件包括一个主体和几个引脚;全加器包含引脚a、b、cin、cout和sum。如果以这个全加器为规范,可以创建许多这种类型的实例。重复经常使用的部分通常很有帮助,例如,当从n个全加器创建一个n位加法器时。

6、设计抽象

建模级别

设计抽象对于硬件系统的开发至关重要。为监督设计过程并确保实现速度和功耗等关键设计目标,硬件设计人员采用了多种设计抽象层。逻辑门是设计抽象的最基本图示。用于构造门的非线性电路被简化为逻辑门,它只接受二进制布尔值。当用逻辑门表示时,一些设计工作(例如准确的延迟计算)变得困难或不可能。其他设计活动,如逻辑优化,太费力而无法在电路上进行。选择最适合设计任务的设计抽象。

更高的抽象也可用于使用更精确的模型来改进初始决策。例如,经常使用直接的延迟计算来优化逻辑,然后再使用精确的电路数据改进逻辑设计。层次结构和设计抽象是不一样的。例如,由布尔逻辑函数构成的架构使用与设计层次结构中使用的组件具有相同抽象程度的组件。订单的每个级别都通过引入更多组件来增加复杂性。由于它被重铸为较低的抽象级别,因此组件的数量可能不会改变;这些组件的更复杂行为增加了复杂性。

7、自上而下和自下而上的设计

设计总是需要从最不抽象的描述开始,从抽象层次的顶部开始下降。向抽象中添加有用的信息必须是设计过程的第一步。然而,自上而下的设计选择是在对每个抽象级别可用的备选方案知之甚少的情况下做出的。希望选择最能满足的速度、面积和功率需求的候选者。

在进行早期设计之前,无法准确估算此类费用。自下而上的分析和设计将成本信息传播到更高的抽象层次;例如,可能会使用来自电路设计的更精确的延迟信息来重新设计逻辑。在完成实施之前,经验将帮助估算费用,但大多数设计都需要自上而下的设计循环,然后是自下而上的重新设计。